For a long time I have been using the AVR port of FreeRTOS as the platform for my Arduino hardware habit. I’ve written (acquired, stolen, and corrupted) a plethora of different drivers and solutions for the various projects I’ve built over the last years. But, sometimes it would be nice to just try out a new piece of hardware in a solid multi-tasking environment without having to dive into the datasheets and write code. Also, when time is of the essence rewriting someone’s existing driver is just asking for stress and failure.

So recently, with an important hack-a-thon coming up, I thought it would be nice to build a robust FreeRTOS implementation that can just shim into the Arduino IDE and allow me to use the best parts of both environments, seamlessly.

Arduino IDE Core is just AVR

One of the good things about the Arduino core environment is that it is just the normal AVR environment with a simple Java IDE added. That means that all of the AVR command line tools used to build Arduino sketches will also just work my AVR port of FreeRTOS.

Some key aspects of the AVR FreeRTOS port have been adjusted to create the seamless integration with the Arduino IDE. These optimizations are not necessarily the best use of FreeRTOS, but they make the integration much easier.

FreeRTOS needs to have an interrupt timer to trigger the scheduler to check which task should be using the CPU, and to fairly distribute processing time among equivalent priority tasks. In the case of the Arduino environment all of the normal timers are configured in advance, and therefore are not available for use as the system_tick timer. However, all AVR ATmega devices have a watchdog timer which is driven by an independent 128kHz internal oscillator. Arduino doesn’t configure the watchdog timer, and conveniently the watchdog configuration is identical across the entire ATmega range. That means that the entire range of classic AVR based Arduino boards can be supported within FreeRTOS with one system_tick configuration.

The Arduino environment has only two entry point functions available for the user, setup() and loop(). These functions are written into an .ino file and are linked together with and into a main() function present in the Arduino libraries. The presence of a fixed main() function within the Arduino libraries makes it really easy to shim FreeRTOS into the environment.

The main() function in the main.c file contains a initVariant() weak attribute stub function prior to the internal Arduino initialisation setup() function. By implementing an initVariant() function execution can be diverted into the FreeRTOS environment, after calling the normal setup() initialisation, by simply continuing to start the FreeRTOS scheduler.

int main(void) // Normal Arduino main.cpp. Normal execution order.

{

init();

initVariant(); // Our initVariant() diverts execution from here.

setup(); // The Arduino setup() function.

for (;;)

{

loop(); // The Arduino loop() function.

if (serialEventRun) serialEventRun();

}

return 0;

}

Firstly, this initVariant() function is located in the variantHooks.cpp file in the FreeRTOS library. It replaces the weak attribute function definition in the Arduino core.

void initVariant(void)

{

setup(); // The Arduino setup() function.

vTaskStartScheduler(); // Initialise and run the FreeRTOS scheduler. Execution should never return to here.

}

Secondly, the FreeRTOS idle task is used to run the loop() function whenever there is no unblocked FreeRTOS task available to run. In the trivial case, where there are no configured FreeRTOS tasks, the loop() function will be run exactly as normal, with the exception that a short scheduler interrupt will occur every 15 milli-seconds (configurable). This function is located in the variantHooks.cpp file in the library.

void vApplicationIdleHook( void )

{

loop(); // The Arduino loop() function.

if (serialEventRun) serialEventRun();

}

Putting these small changes into the Arduino IDE, together with a single directory containing the necessary FreeRTOS v10.x.x files configured for AVR, is all that needs to be done to slide the FreeRTOS shim under the Arduino environment.

I have published the relevant files on Github where the commits can be browsed and the repository downloaded. The simpler solution is to install FreeRTOS using the Arduino Library Manager, or download the ZIP files from Github and install manually as a library in your Arduino IDE.

Getting Started with FreeRTOS

Ok, with these simple additions to the Arduino IDE via a normal Arduino library, we can get started.

Firstly in the Arduino IDE Library manager, from Version 1.6.8, look for the FreeRTOS library under the Type: “Contributed” and the Topic: “Timing”.

Arduino Library Manager

Arduino Library ManagerEnsure that the most recent FreeRTOS library is installed. As of writing that is v10.3.0-4.

Example of FreeRTOS v8.2.3-6 Installed

Example of FreeRTOS v8.2.3-6 InstalledThen under the Sketch->Include Library menu, ensure that the FreeRTOS library is included in your sketch. A new empty sketch will look like this.

Compile and upload this empty sketch. This will show you how much of your flash is consumed by the FreeRTOS scheduler. As a guide the following information was compiled using Arduino v1.8.5 on Windows 10.

// Device: loop() -> FreeRTOS | Additional Program Storage // Uno: 444 -> 6592 | 20% // Goldilocks: 502 -> 6684 | 5% // Leonardo: 3462 -> 9586 | 23% // Yun: 3456 -> 9580 | 23% // Mega: 662 -> 6898 | 2%

Now test and upload the Blink sketch, with an underlying Real-Time Operating System. That’s all there is to having FreeRTOS running in your sketches. So simple.

Next Steps

Blink_AnalogRead.ino is a good way to take the next step as it combines two basic Arduino examples, Blink and AnalogRead into one sketch with in two separate tasks. Both tasks perform their duties, managed by the FreeRTOS scheduler.

#include <Arduino_FreeRTOS.h>

// define two tasks for Blink and AnalogRead

void TaskBlink( void *pvParameters );

void TaskAnalogRead( void *pvParameters );

// the setup function runs once when you press reset or power the board

void setup()

{

// Now set up two tasks to run independently.

xTaskCreate(

TaskBlink

, "Blink" // A name just for humans

, 128 // This stack size can be checked and adjusted by reading the Stack Highwater

, NULL

, 2 // Priority, with 3 (configMAX_PRIORITIES - 1) being the highest, and 0 being the lowest.

, NULL );

xTaskCreate(

TaskAnalogRead

, "AnalogRead"

, 128 // Stack size

, NULL

, 1 // Priority, with 3 (configMAX_PRIORITIES - 1) being the highest, and 0 being the lowest.

, NULL );

// Now the task scheduler, which takes over control of scheduling individual tasks, is automatically started.

}

void loop()

{

// Empty. Things are done in Tasks. Never Block or delay.

}

/*--------------------------------------------------*/

/*---------------------- Tasks ---------------------*/

/*--------------------------------------------------*/

void TaskBlink(void *pvParameters) // This is a task.

{

(void) pvParameters;

// initialize digital pin 13 as an output.

pinMode(13, OUTPUT);

for (;;) // A Task shall never return or exit.

{

digitalWrite(13, HIGH); // turn the LED on (HIGH is the voltage level)

vTaskDelay( 1000 / portTICK_PERIOD_MS ); // wait for one second

digitalWrite(13, LOW); // turn the LED off by making the voltage LOW

vTaskDelay( 1000 / portTICK_PERIOD_MS ); // wait for one second

}

}

void TaskAnalogRead(void *pvParameters) // This is a task.

{

(void) pvParameters;

// initialize serial communication at 9600 bits per second:

Serial.begin(9600);

for (;;)

{

// read the input on analog pin 0:

int sensorValue = analogRead(A0);

// print out the value you read:

Serial.println(sensorValue);

vTaskDelay(1); // one tick delay (15ms) in between reads for stability

}

}

Next there are a number of examples in the FreeRTOS Quick Start Guide.

One last important thing you can do is to reduce device power consumption by not using the default loop() function for anything more than putting the MCU to sleep. This code below can be used for simply putting the MCU into a sleep mode of your choice, while no tasks are unblocked. Remember that the loop() function shouldn’t ever disable interrupts and block processing.

#include <avr/sleep.h> // include the Arduino (AVR) sleep functions.

loop() // Remember that loop() is simply the FreeRTOS idle task. Something to do, when there's nothing else to do.

{

// Digital Input Disable on Analogue Pins

// When this bit is written logic one, the digital input buffer on the corresponding ADC pin is disabled.

// The corresponding PIN Register bit will always read as zero when this bit is set. When an

// analogue signal is applied to the ADC7..0 pin and the digital input from this pin is not needed, this

// bit should be written logic one to reduce power consumption in the digital input buffer.

#if defined(__AVR_ATmega640__) || defined(__AVR_ATmega1280__) || defined(__AVR_ATmega1281__) || defined(__AVR_ATmega2560__) || defined(__AVR_ATmega2561__) // Mega with 2560

DIDR0 = 0xFF;

DIDR2 = 0xFF;

#elif defined(__AVR_ATmega644P__) || defined(__AVR_ATmega644PA__) || defined(__AVR_ATmega1284P__) || defined(__AVR_ATmega1284PA__) // Goldilocks with 1284p

DIDR0 = 0xFF;

#elif defined(__AVR_ATmega328P__) || defined(__AVR_ATmega168__) || defined(__AVR_ATmega8__) // assume we're using an Arduino with 328p

DIDR0 = 0x3F;

#elif defined(__AVR_ATmega32U4__) || defined(__AVR_ATmega16U4__) // assume we're using an Arduino Leonardo with 32u4

DIDR0 = 0xF3;

DIDR2 = 0x3F;

#endif

// Analogue Comparator Disable

// When the ACD bit is written logic one, the power to the Analogue Comparator is switched off.

// This bit can be set at any time to turn off the Analogue Comparator.

// This will reduce power consumption in Active and Idle mode.

// When changing the ACD bit, the Analogue Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR.

// Otherwise an interrupt can occur when the ACD bit is changed.

ACSR &= ~_BV(ACIE);

ACSR |= _BV(ACD);

// There are several macros provided in the header file to actually put

// the device into sleep mode.

// SLEEP_MODE_IDLE (0)

// SLEEP_MODE_ADC (_BV(SM0))

// SLEEP_MODE_PWR_DOWN (_BV(SM1))

// SLEEP_MODE_PWR_SAVE (_BV(SM0) | _BV(SM1))

// SLEEP_MODE_STANDBY (_BV(SM1) | _BV(SM2))

// SLEEP_MODE_EXT_STANDBY (_BV(SM0) | _BV(SM1) | _BV(SM2))

set_sleep_mode( SLEEP_MODE_IDLE );

portENTER_CRITICAL();

sleep_enable();

// Only if there is support to disable the brown-out detection.

#if defined(BODS) && defined(BODSE)

sleep_bod_disable();

#endif

portEXIT_CRITICAL();

sleep_cpu(); // good night.

// Ugh. I've been woken up. Better disable sleep mode.

sleep_reset(); // sleep_reset is faster than sleep_disable() because it clears all sleep_mode() bits.

}

o that’s all there is to it. There’s nothing more to do except to read the FreeRTOS Quick Start Guide.

Further reading with manicbug, and by searching on this site too.

General Usage

FreeRTOS has a multitude of configuration options, which can be specified from within the FreeRTOSConfig.h file. To keep commonality with all of the Arduino hardware options, some sensible defaults have been selected.

The AVR Watchdog Timer is used with to generate 15ms time slices, but Tasks that finish before their allocated time will hand execution back to the Scheduler. This does not affect the use of any of the normal Timer functions in Arduino.

Time slices can be selected from 15ms up to 500ms. Slower time slicing can allow the Arduino MCU to sleep for longer, without the complexity of a Tickless idle.

Watchdog period options:

- WDTO_15MS

- WDTO_30MS

- WDTO_60MS

- WDTO_120MS

- WDTO_250MS

- WDTO_500MS

Note that Timer resolution is affected by integer math division and the time slice selected. Trying to accurately measure 100ms, using a 60ms time slice for example, won’t work.

Stack for the loop() function has been set at 192 bytes. This can be configured by adjusting the configIDLE_STACK_SIZE parameter. It should not be less than the configMINIMAL_STACK_SIZE. If you have stack overflow issues, just increase it. Users should prefer to allocate larger structures, arrays, or buffers using pvPortMalloc(), rather than defining them locally on the stack. Or, just declare them as global variables.

Memory for the heap is allocated by the normal malloc() function, wrapped by pvPortMalloc(). This option has been selected because it is automatically adjusted to use the capabilities of each device. Other heap allocation schemes are supported by FreeRTOS, and they can used with additional configuration.

Never use the Arduino delay() function in your Tasks, as it burns CPU cycles and doesn’t place the Task into Blocked State, allowing the Scheduler to place other lower priority tasks into Running State. Use vTaskDelay() or vTaskDelayUntil() instead. Also never delay or Block the Arduino loop() as this is being run by the FreeRTOS Idle Task, which must never be blocked.

Errors

- Stack Overflow: If any stack (for the loop() or) for any Task overflows, there will be a slow LED blink, with 4 second cycle.

- Heap Overflow: If any Task tries to allocate memory and that allocation fails, there will be a fast LED blink, with 100 millisecond cycle.

Compatibility

- ATmega328 @ 16MHz : Arduino UNO, Arduino Duemilanove, Arduino Diecimila, etc.

- ATmega328 @ 16MHz : Adafruit Pro Trinket 5V, Adafruit Metro 328, Adafruit Metro Mini

- ATmega328 @ 16MHz : Seeed Studio Stalker

- ATmega328 @ 16MHz : Freetronics Eleven, Freetronics 2010

- ATmega328 @ 12MHz : Adafruit Pro Trinket 3V

- ATmega32u4 @ 16MHz : Arduino Leonardo, Arduino Micro, Arduino Yun, Teensy 2.0

- ATmega32u4 @ 8MHz : Adafruit Flora, Bluefruit Micro

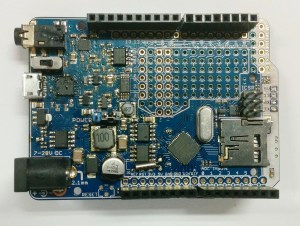

- ATmega1284p @ 20MHz : Freetronics Goldilocks V1

- ATmega1284p @ 24.576MHz : Seeed Studio Goldilocks V2, Seeed Studio Goldilocks Analogue

- ATmega2560 @ 16MHz : Arduino Mega, Arduino ADK

- ATmega2560 @ 16MHz : Freetronics EtherMega

- ATmega2560 @ 16MHz : Seeed Studio ADK

- ATmegaXXXX @ XXMHz : Anything with an ATmega MCU, really.

Files and Configuration

- Arduino_FreeRTOS.h : Must always be #include first. It references other configuration files, and sets defaults where necessary.

- FreeRTOSConfig.h : Contains a multitude of API and environment configurations.

- FreeRTOSVariant.h : Contains the AVR specific configurations for this port of FreeRTOS.

- heap_3.c : Contains the heap allocation scheme based on malloc(). Other schemes are available and can be substituted (heap_1.c, heap_2.c, heap_4.c, and heap_5.c) to get a smaller binary file, but they depend on user configuration for specific MCU choice.